28V 功率 pmos 驱动&2 路栅调&3 路漏调

TR 电源管理芯片

### 1. 产品特性

- ▶ 28V 功率 PMOS 驱动

- ➤ PA 发射电源调制, 5V/500mA

- ▶ DRV 收发电源调制, 5V/200mA

- ➤ LNA 接收电源调制, 5V/200mA

- ➤ GaN 栅压调节, -1.7V~-3.2V

- ➤ GaAs 栅压调节, -0.3V ~ -0.65V

- ➤ GaN 栅极驱动电流±50mA

- ➤ GaAs 栅极驱动电流±10mA

- ▶ 正负压欠压锁定

- ▶ T信号过脉宽保护

## 2. 功能描述

C49020S是一款多功能射频电源调制器芯片,主要由28V PMOS功率管驱动电路,发射、接收、公共支路电源调制电路和GaAs、GaN栅压调节电路这三部分电路构成。其中PMOS功率管驱动电路为高速、低延迟驱动电路,具有负压电源监控及使能控制开断功能、漏极快速放电功能、过脉宽保护功能。发射、接收、公共支路电源为VDD,内置功率PMOS,由T/R信号直接控制开关。栅压调制控制电路由GaAs、GaN栅极调制共两路构成,GaAs由3位控制位对输出电压选择,GaN由4位控制位对输出电压选择,以实现栅压可调。

## 3. 产品应用

- ▶ 射频驱动放大器供电

- ▶ 28V功率PMOS驱动

- ➤ GaAs/GaN栅极调制驱动

## 4. 裸芯片/封装简介

▶ 本产品采用QFN 5\*5-40封装

## 5. 绝对最大额定值

表 1 绝对最大额定值

| 符号           | 参数          | 最小值 | 最大值 | 单位 |

|--------------|-------------|-----|-----|----|

| $V_{ m HI}$  | PMOS功率管驱动电源 |     | 36  | V  |

| $V_{ m DD}$  | 正电源电压       |     | 6   | V  |

| $ m V_{EE}$  | 负电源电压       |     | -6  | V  |

| $T_{ m STG}$ | 储存温度        | -65 | 150 | °C |

| $T_{A}$      | 工作温度        | -55 | 125 | °C |

(1) 使用中超过这些绝对最大值可能对芯片造成永久损坏。

## 6. 推荐工作条件

1) 电源电压 V<sub>HI</sub>: 9V~36V

2) 电源电压 V<sub>DD</sub>: 4.5V~5.5V

3) 电源电压 VEE: -5.5V ~ -4.5V

4) 工作环境温度: -55℃~125℃

## 7. 主要电参数

除非特别说明, T<sub>A</sub>= -55℃~125℃, V<sub>HI</sub>=28V, V<sub>DD</sub>=5V, V<sub>EE</sub>=-5V。

表 2 主要电参数

| 参数       | 符号               | 测试条件                   | 最小值  | 典型值  | 最大值 | 单位 |

|----------|------------------|------------------------|------|------|-----|----|

| VHI 静态电流 | I <sub>VHI</sub> | V <sub>HI</sub> =28V   |      | 0.15 | 1   | mA |

| VDD 静态电流 | $I_{VDD}$        | V <sub>DD</sub> =5V    |      | 0.1  | 1   | mA |

| VEE 静态电流 | $I_{ m VEE}$     | $V_{EE} = -5V$         |      | 0.55 | 1.5 | mA |

| 输入高电平    | $V_{H}$          |                        | 2.4  |      |     | V  |

| 输入低电平    | $V_{\rm L}$      |                        |      |      | 0.8 | V  |

| 输入漏电流    | $I_{\rm IN}$     | TTL=0V/5V              |      |      | 10  | uA |

| TO 输出高电平 | ТОн              | I <sub>OH</sub> =-20mA | 27.9 |      |     | V  |

| TO 输出低电平 | $TO_L$           | I <sub>OL</sub> =20mA  | 16   |      | 19  | V  |

| PD 输出低电平     | $PD_L$               | I <sub>PD</sub> =20mA                  |       |    | 0.15  | V  |

|--------------|----------------------|----------------------------------------|-------|----|-------|----|

| TXO 输出高电平    | ТХОн                 | $I_O = -500 \text{mA}$                 | 4.85  |    |       | V  |

| TRX 输出高电平    | TRXO <sub>H</sub>    | $I_O = -200 \text{mA}$                 | 4.9   |    |       | V  |

| RXO 高电平      | $RXO_H$              | $I_O = -200 \text{mA}$                 | 4.9   |    |       | V  |

| VG1 输出电平     | VG1                  | I <sub>O</sub> =±50mA, D[3:0]=0000     | -1.79 |    | -1.61 | V  |

| VG2 输出电平     | VG2                  | I <sub>O</sub> =±10mA, D[6:4]=000      | -0.69 |    | -0.61 | V  |

| TO 开通/关闭时间   | t <sub>TO_ON</sub>   | 负载电容≤3nF                               |       | 30 | 100   | ns |

| TXO 开通/关闭时间  | t <sub>TXO_ON</sub>  | $I_{O} = -200 \text{mA} (1 \text{nF})$ |       | 50 | 100   | ns |

| TRXO 开通/关闭时间 | t <sub>TRXO_ON</sub> | $I_{O} = -100 \text{mA} (1 \text{nF})$ | X     | 50 | 100   | ns |

| RXO 开通/关闭时间  | t <sub>RXO_ON</sub>  | $I_{O} = -100 \text{mA} (1 \text{nF})$ | X     | 50 | 100   | ns |

# 8. 功能框图及引脚介绍

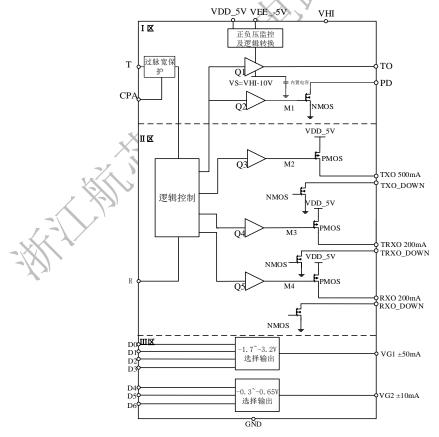

## 8.1 功能框图

图 1 功能框图

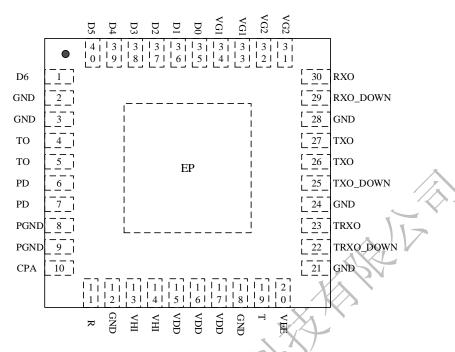

## 8.2 引脚介绍

图 2 引脚分布图(俯视图)

表 3 引脚功能说明

| 序号 | 符号   | 功能                   |

|----|------|----------------------|

| 1  | D6   | GaAs 栅压调节位           |

| 2  | GND  | 接地                   |

| 3  | GND  | 按地                   |

| 4  | TO   | 外置 PMOS 栅极驱动输出       |

| 5  | ТО   | ク 「. <u></u>         |

| 6  | PD   | 外置 PMOS 漏极泄电端口       |

| 7  | PD   | 沙上直. I MIOS /确似在电池测口 |

| 8  | PGND | 接功率地                 |

| 9  | PGND | 按切平地                 |

| 10 | СРА  | 过脉宽保护时间设定脚           |

| 11 | R    | 接收调制 TTL 输入          |

| 12 | GND  | 接地                   |

| 13 | VHI  | . 2027 中海            |

| 14 | VHI  | +28V 电源              |

| 15 | VDD  |                      |

| 16 | VDD  | +5V 电源               |

| 17 | VDD  |                      |

| 18 | GND       | 接地                                                 |

|----|-----------|----------------------------------------------------|

| 19 | Т         | 发射调制 TTL 输入                                        |

| 20 | VEE       | -5V 电源                                             |

| 21 | GND       | 接地                                                 |

| 22 | TRXO_DOWN | 公共支路输出泄电端口                                         |

| 23 | TRXO      | 公共支路+5V 输出                                         |

| 24 | GND       | 接地                                                 |

| 25 | TXO_DOWN  | 发射调制输出泄电端口                                         |

| 26 | TXO       | 发射调制+5V 输出                                         |

| 27 | TXO       | 及别师明+3 V 制田                                        |

| 28 | GND       | 接地                                                 |

| 29 | RXO_DOWN  | 接收调制输出泄电端口                                         |

| 30 | RXO       | 接收调制+5V 输出                                         |

| 31 | VG2       | GaAs 栅压输出-0.3V ~ -0.65V                            |

| 32 | VG2       | UaAs mil / Li mi                                   |

| 33 | VG1       | GaN 栅压输出-1.7V ~ -3.2V                              |

| 34 | VG1       | Oatv /ш/.Eпі Щ-1.7 v ~ -3.2 v                      |

| 35 | D0        | GaN 栅压调节位                                          |

| 36 | D1        | GaN 栅压调节位                                          |

| 37 | D2        | GaN 栅压调节位                                          |

| 38 | D3        | GaN 栅压调节位                                          |

| 39 | D4        | GaAs 栅压调节位                                         |

| 40 | D5        | GaAs 栅压调节位                                         |

|    | EP        | 热沉。位于芯片底部,与 VEE 电气连接, <b>请勿直接通</b><br>过此脚输入-5V 电压。 |

## 9. 逻辑功能说明

▶ 逻辑关系真值表中,"0"指0V,"1"指5V。

#### 9.1 PMOS 驱动电路 (I区)

PMOS驱动电路为高速、低延迟驱动电路,具有负压电源监控及使能控制开断功能、漏极快速放电功能,供电单元为VHI。

#### 9.1.1 负压电源监控逻辑

负压监测门限值为-3V,阈值范围为±0.5V,即当V<sub>EE</sub><-3.5V时,驱动器Q1使能有效,TO正常逻辑输

出; 当VEE>-2.5V时,驱动器Q1使能无效,TO为固定值28V,其逻辑关系见下表:

| VEE    | Q1 使能状态 |

|--------|---------|

| <-3.5V | 有效      |

| >-2.5V | 无效      |

表 4 负压检测使能表

▶ 引脚PD与TO后级驱动的PMOS的漏极直接连接。

#### 9.1.2 T通道逻辑

当T为高电平时,M1管关断,TO输出低电平V<sub>S</sub>=V<sub>HI</sub>-10V,TO可开启外围PMOS;当T为低电平时,M1管打开,TO输出高电平,TO可关断外围PMOS,同时外围PMOS的漏极可通过M1管进行快速放电,满足使用过程中对放电时间的要求。同时,T信号具有过脉宽保护功能,由CPA引脚对地外接电容调制保护时间,1nF电容对应过脉宽保护阈值为1ms,T信号脉宽达到保护阈值时内部会将其关断。

| 输   | λ   | 输出      |

|-----|-----|---------|

| VEE | T   | ТО      |

| 0   | 0   | VHI     |

| 0   | XL1 | VHI     |

| -5  | 0   | VHI     |

| -5  | 1   | VHI-10V |

表 5 T通道逻辑和负压检测关系表

注: 当 VHI<10V, TO 为低时输出约为 1V。

#### 9.2 电源开关控制电路(II区)

电源开关控制电路供电单元为VDD,内置PMOS,其由T/R信号直接控制。如芯片框图所示,T/R信号和TXO、RXO、TRXO、TXO\_DOWN、RXO\_DOWN、TRXO\_DOWN的逻辑关系见下表

| T | R | TXO | TXO_DOWN | TRX | TRX_DOWN | RXO | RXO_DOWN |

|---|---|-----|----------|-----|----------|-----|----------|

| 0 | 0 | 高阻态 | 0        | 高阻态 | 0        | 高阻态 | 0        |

| 0 | 1 | 高阻态 | 0        | 1   | 高阻态      | 1   | 高阻态      |

| 1 | 0 | 1   | 高阻态      | 1   | 高阻态      | 高阻态 | 0        |

| 1 | 1 | 高阻态 | 0        | 高阻态 | 0        | 高阻态 | 0        |

表 6 T/R 控制逻辑关系表

#### 9.3 栅压调制控制电路(III区)

栅压调制电路有两路,其中GaN栅压调制控制电路输出端为VG1,范围为-1.7V~-3.2V; GaAs栅压调制控制电路输出端为VG2, 范围为-0.3V~-0.65V。

#### 9.3.1 GaN栅压调制控制逻辑关系

GaN栅压调制控制电路由4位控制位对输出电压进行选择,VG1默认态为0000(-1.7V),若需置1请连接至5V,其逻辑关系见下表7

| D3 | D2    | D1  | D0 | VG1    |

|----|-------|-----|----|--------|

| 0  | 0     | 0   | 0  | -1.70V |

| 0  | 0     | 0   | 1  | -1.80V |

| 0  | 0     | 1   | 0  | -1.90V |

| 0  | 0     | 1   | 1  | -2.00V |

| 0  | 1     | 0   | 0  | -2.10V |

| 0  | 1     | 0   | XI | -2.20V |

| 0  | 1     | 1   | 0  | -2.30V |

| 0  | 1     | 1   | 1  | -2.40V |

| 1  | 0     | 0   | 0  | -2.50V |

| 1  | 0     | 0   | 1  | -2.60V |

| 1  | 0     | XLi | 0  | -2.70V |

| 1  | 0     | 1   | 1  | -2.80V |

| 1  | 1/2   | 0   | 0  | -2.90V |

| 1  |       | 0   | 1  | -3.00V |

| 1  | x = 1 | 1   | 0  | -3.10V |

| 1  | 1     | 1   | 1  | -3.20V |

表 7 GaN 栅压调制控制逻辑关系表

#### 9.3.2 GaAs栅压调制控制逻辑关系

GaAs驱动放大器栅压调制控制电路由3位控制位对输出电压进行选择,VG2默认态为000(-0.65V),若需置1请连接至5V,其逻辑关系见下表8

| D4 | D5 | D6 | VG2    |

|----|----|----|--------|

| 0  | 0  | 0  | -0.65V |

| 0  | 0  | 1  | -0.60V |

| 0  | 1  | 0  | -0.55V |

| 0  | 1  | 1  | -0.50V |

表 8 GaAs 栅压调制控制逻辑关系表

| 1 | 0 | 0 | -0.45V |

|---|---|---|--------|

| 1 | 0 | 1 | -0.40V |

| 1 | 1 | 0 | -0.35V |

| 1 | 1 | 1 | -0.30V |

#### 10. 芯片应用说明

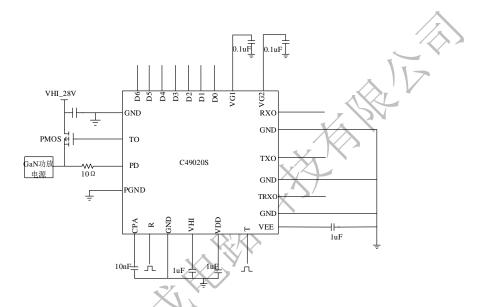

#### 10.1 典型应用图

图 3 C49020S 工作推荐电路

➤ 所用PMOS漏极电压为28V, Vth<10V

#### 10.2 应用说明

- (1) VHI、VDD、VEE 分别接+28V、+5V、-5V 的电压;

- (2) T、R 分别为发射、接收调制 TTL 输入信号, 其高电平范围 2.4V~5V, 低电平电压范围 0~0.8V;

- (3) VG1 接 GaN 功放的栅极, 供电不能超过 50mA, 可通过 D0~D3 进行-1.7V~-3.2V 范围的选择;

- (4) VG2 接 GaAs 驱放的栅极, 供电不能超过 10mA, 可通过 D4~D6 进行-0.3V~-0.65V 范围的选择;

- (5) RXO与RXO\_DOWN 相连后接 200mA 以下低噪放的电源;

- (6) TXO 与 TXO\_DOWN 相连后接 500mA 以下 GaAs 驱放的电源;

- (7) TRXO 与 TRXO\_DOWN 相连后接 200mA 以下多功能芯片放大器的电源;

- (8) TO 接 PMOS 的栅极, 当 T 为高时, TO 输出 18V, PMOS 导通; 当 T 为低时, TO 输出 28V, PMOS 关断;

- (9) PD接PMOS的漏极,当PMOS关断时,该端口提供从PMOS漏端到地的泄放通道,使PMOS漏端快速放电。

(10) CPA 引脚外接 1nF 电容过脉宽保护时间为 1ms,外接 10nF 电容时过脉宽保护为 10ms。若不使用过脉宽保护功能时, CPA 引脚需接地。下面给出不同 CPA 电容下对应的过脉宽保护时间

| - K / CIII/I/IX LI II | 7 2 CM 20 11 11 11 11 11 11 11 11 11 11 11 11 11 |  |

|-----------------------|--------------------------------------------------|--|

| CPA 外接电容值             | 过脉宽保护时间                                          |  |

| 100pF                 | 90~110μs                                         |  |

| 130 pF                | 140~170μs                                        |  |

| 560pF                 | 520~560μs                                        |  |

| 1nF                   | 0.9~1.16ms                                       |  |

| 10nF                  | 8~12ms                                           |  |

表 9 CPA 外接电容值与过脉宽保护时间对照

### 11. 注意事项

#### 11.1 使用注意事项

- (1) T、R、D0~D6端口内部设计有下拉电阻,不用时可悬空,状态为低;

- (2) 器件不能超过极限工作条件使用;

- (3) 电源去耦:应在靠近器件电源引出端处采用大于等于 1μμ 电容。此外,线路板布线应尽量短,尽量避免直角、锐角走线;

- (4) 电路使用时应先接电源端,再接输入端,**电源端建议按照 VEE、VDD、VHI 的顺序上电,按照 VHI、VDD、VEE 的顺序下电**,同时应尽量避免电源、地线上的干扰;

- (5) 工作时先检查电源、地是否接触良好后再接通器件电源。

#### 11.2 防护注意事项

- (6) 本产品可以抗 1000V 静电击穿,使用时应注意避免静电损伤,操作人员戴接地防静电手环,操作台面、操作设备接地良好,拿取芯片时,最好使用真空吸笔,以免损伤芯片;

- (7) 真空包装好的芯片应贮存在温度 10℃到 30℃,相对湿度 20%~70%的环境中,周围没有酸、碱或者其它腐蚀气体,通风良好,且具备相应防静电措施,未使用的芯片应存于氮气柜中;

- (8) 在避免雨、雪直接影响的条件下,装有产品的包装箱可以用安全的运输工具运输。但不能和带有酸性、碱性和其它腐蚀性物体堆放在一起。

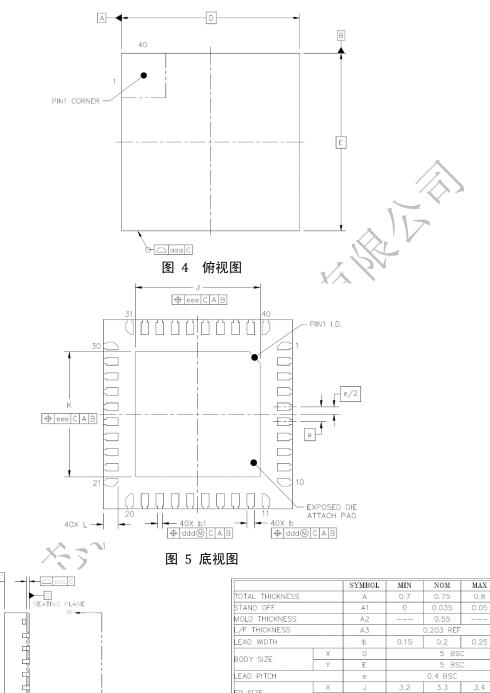

# 12. 芯片外形尺寸

| SEATING PLANE |  |  |  |

|---------------|--|--|--|

|               |  |  |  |

|               |  |  |  |

| l 🖷           |  |  |  |

|               |  |  |  |

|               |  |  |  |

| <del></del>   |  |  |  |

|               |  |  |  |

|               |  |  |  |

|               |  |  |  |

|               |  |  |  |

|               |  |  |  |

| M             |  |  |  |

| A1 (A3)       |  |  |  |

| A -           |  |  |  |

| 图 6 侧视图       |  |  |  |

|               |  |  |  |

|                        |                  | SYMBOL | MIN       | NOM   | MAX   |

|------------------------|------------------|--------|-----------|-------|-------|

| TOTAL THICKNESS        |                  | А      | 0.7       | 0.75  | 0.8   |

| STAND OFF              |                  | A1     | 0         | 0.035 | 0.05  |

| MOLD THICKNESS         |                  | A2     |           | 0.55  |       |

| L/F THICKNESS          |                  | А3     | 0.203 REF |       |       |

| LEAD WIDTH             |                  | b      | 0.15      | 0.2   | 0.25  |

| BODY SIZE              | X                | D      | 5 BSC     |       |       |

| BODT SIZE              | Υ                | Е      | 5 BSC     |       |       |

| LEAD PITCH             |                  | е      | 0.4 BSC   |       |       |

| EP SIZE                | X                | J      | 3.2       | 3.3   | 3.4   |

| EP SIZE                | Υ                | K      | 3.2       | 3.3   | 3.4   |

| LEAD LENGTH            |                  | L      | 0.35      | 0.4   | 0.45  |

| PACKAGE EDGE TOLERANCE |                  | aaa    | 0.1       |       |       |

| MOLD FLATNESS          |                  | bbb    | 0.1       |       |       |

| COPLANARITY            |                  | ccc    | 0.08      |       |       |

| LEAD OFFSET            |                  | ddd    | 0.1       |       |       |

| EXPOSED PAD OFFSE      | POSED PAD OFFSET |        | 0.1       |       |       |

| LEAD WIDTH             |                  | b1     | 0.075     | 0.125 | 0.175 |

|                        |                  |        |           |       |       |

|                        |                  |        |           |       |       |

|                        |                  |        |           |       |       |

|                        |                  |        |           |       |       |

## 13. 版本说明

| 产品型号    | 编制时间       | 版本编号  | 修订记录 |

|---------|------------|-------|------|

| C49020S | 2022.07.08 | Rev.1 | 初始版本 |

|         |            |       |      |